Hur man skapar en enkel seriell UART-sändare i verilog HDL

De flesta Universal Asynchronous Receiver Transmitter (UART) som jag hittade online är för komplicerade och svåra att förstå, här kommer jag att förklara en enkel teori och även kod för hur man bygger en.

Låt oss först prata om hur sändare fungerar. Grundprincipen är att skicka flera databitar över en enda rad. I vår sändare är dessa data parallella, men för att minska antalet ledningar som krävs använder vi seriell kommunikation som omvandlas till parallell vid mottagningsänden.

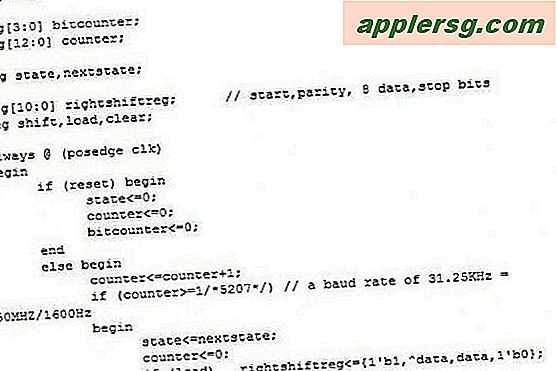

De grundläggande sakerna vi behöver är följande:

- En klockavdelare (vår räknare)

Detta gör det möjligt för oss att skicka data med en viss hastighet (baudhastighet). Vår mottagare kommer att prova och ta data bit för bit.

- Ett skiftregister

Vi behöver veta hur många bitar åt gången vi sänder, vårt skiftregister kommer att ha en startbit, databitar, paritetsbit (valfritt), slutbit.

- Ett tillståndsdiagram

Innan vi skriver någon kod måste vi tänka på vad vi behöver skapa och det bästa sättet är att skapa ett tillståndsdiagram över vår design. Vi vet att för en sändare behöver vi två tillstånd, tomgång och sändning.

Efter att ha fått ett tillståndsdiagram kan vi nu beräkna vad vår räknare kommer att vara. Detta görs med:

räknare = FPGA klockhastighet / överföringshastighet

I det här exemplet använder jag en överföringshastighet på 9600, vilket gör min räknare = 5208.

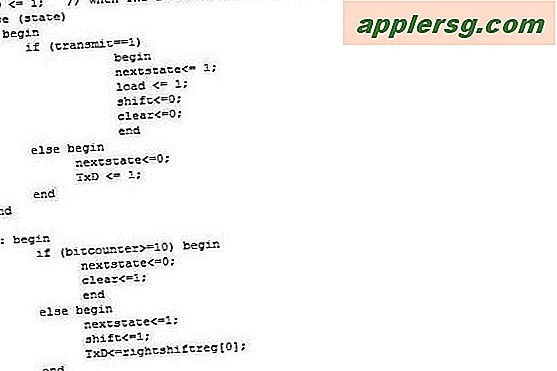

Sist beräknar vi vårt skiftregister och slutar skriva vår statsmaskin. I min provkod använder jag en startbit, paritetsbit, 8 bitar data och slutbit. Detta är 11 bitar totalt.

Båda bilderna i steg 2 och 3 tillsammans i samma modul kompletterar vår sändarkod som krävs för att programmera till FPGA. Den här koden fungerar med en annan FPGA som är ansluten seriellt eller med Windows hyperterminal bland andra hårdvaror. Kan lätt modifieras för att arbeta med mycket mer.

Slutligen skapar vi en testarmatur för att åtgärda eventuella fel och simulera vårt program innan vi programmerar FPGA.

Detta avslutar sändaren. Lämna kommentarer om du har några frågor eller känner att det saknas något här.

Tips

Både sändare och mottagare måste känna till baudhastigheten med vilken data skickas.